Use the five-stage pipeline with forwarding unit.

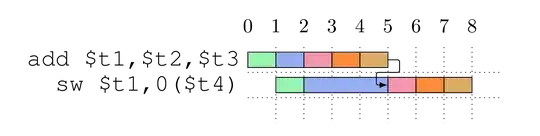

add $t1, $t2, $t3

sw $t1, 0($t4)

In the above code, is the data hazard of t1 fixed by forwarding the correct t1 value from MEM stage to EXE stage?

Also, are there totally four forwarding paths, which are MEMtoEXE, WBtoEXE, MEMtoID, WBtoMEM, in pipeline?

It would be grateful if someone can help. Thank you!